Fraunhofer FIT

04.05.2020, 12:17 Uhr

KI optimiert Leiterplatten

Das Fraunhofer-Institut für Angewandte Informationstechnik FIT kann durch modulare KI-Plattformen Leiterplatten optimal designen und überprüfen – und damit den Aufwand um bis zu 20 Prozent reduzieren.

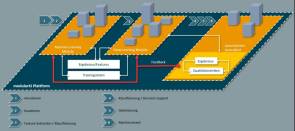

Die modularen Plattformen bestehen aus mehreren Modulen, aus Machine Learning, Deep Learning und Künstlicher Intelligenz. Jedes Modul besteht aus vortrainierten Algorithmen mit verschiedenen Aufgaben. So kann zum Beispiel ein Algorithmus aus der ersten Modulklasse (links) bereits eingehende Daten klassifizieren, als auch aus ihnen Features extrahieren, die wiederum als Input in andere Module fließen.

(Quelle: Fraunhofer FIT)

Die elektronische Revolution der Lebens- und Arbeitswelten wäre ohne sie kaum möglich: Leiterplatten bilden die Basis, auf der kleinste Bauteile miteinander interagieren. Da die Anwendungen immer zahlreicher und komplexer werden, nehmen die Anforderungen an Design und Qualitätssicherung zu – so müssen etwa Interferenzen ausgeschlossen und eine elektromagnetische Verträglichkeit gewährleistet werden. Das Fraunhofer-Institut für Angewandte Informationstechnik FIT kann durch modulare KI-Plattformen Leiterplatten optimal designen und überprüfen – und damit den Aufwand um bis zu 20 Prozent reduzieren.

Leiterbahnen werden so eng und geschickt wie möglich für eine Anwendung geplant, ohne dadurch einen Ausfall zu riskieren. Basis dafür ist bisher das Erfahrungswissen der beteiligten Ingenieure, deren Designs in Versuchen getestet werden müssen. Die Ergebnisse daraus werden zudem nicht stringent dokumentiert, so dass fehleranfällige Designs auch mehrmals Tests durchlaufen. Dieser aufwändige Prozess führt zu hohen Kosten.

Die fertig entwickelten Designs stellen danach hohe Anforderungen an die Produktion. Daher wird jede einzelne Leiterplatte überprüft, zumeist über eine Automatische Optische Inspektion (AOI). Dabei wird über eine Bildanalyse verglichen, ob die Platine so wie geplant produziert wurde, und so technische Fehlstellen detektiert. Dieses Verfahren erzeugt momentan allerdings eine hohe True-negativ-Rate, das heißt, viele funktionierende Platinen werden als fehlerhaft klassifiziert.

Diese müssen dann alle per Hand kontrolliert werden. Dies geschieht sowohl visuell, als auch messtechnisch. Die Überprüfung verursacht wiederum hohe Kosten, denn bei einer zu hohen True-negativ-Rate werden fehlerfrei Bauteile aussortiert. Bei einer zu kleinen Rate sind die Folgekosten durch den Einsatz von Fehlteilen hoch. Eine optimierte True-negativ-Rate durch menschliche Kontrolle ist schwierig, da auch menschliche Schwächen einfließen.

Wie ein zukünftiger Überprüfungsprozess aussehen kann, zeigt die Entwicklung des Fraunhofer FIT. Eine Kamera macht wie bei einer herkömmlichen AOI Aufnahmen von gedruckten Leiterplatten. Daraus wird die Entscheidungsqualität von Algorithmen optimiert. Entscheidend ist dabei die Eingabe qualitativ-hochwertiger Trainingsdaten. Dafür füttern zunächst Experten die Module für Machine Learning und Deep Learning mit einer guten Datenauswahl.

"Diese modulare Bauweise ermöglicht, aneinander gekoppelte Algorithmen einzusetzen, die sich selbst verbessern. Durch laufende automatisierte Kontrollen der Bauteile fließen Daten zurück in den Algorithmus und sind Grundlage für einen Selbstlernprozess im Modul Künstliche Intelligenz", so Timo Brune, Projektleiter beim Fraunhofer FIT. "Dieses permanente Feedbacksystem verbessert die Datengrundlage und optimiert die True-negativ-Rate. Dadurch können nach ersten Schätzungen aus der Industrie rund 20 Prozent an Produktionsressourcen eingespart werden."

Das Training der Module kann der Anwender selbst mit seinen Prozess- und Produktionsdaten übernehmen. Das Unternehmen bleibt so immer im Besitz seiner Daten, die nicht etwa an externe Server geschickt werden müssen. Der "Baukasten" aus Algorithmen kann in beliebiger Kombination auf spezifische Probleme angewandt werden.

Die trainierten Algorithmen lassen sich dann auch bereits beim Design neuer Leiterplatten einsetzen. Die Anordnung von Bauteilen auf der Leiterplatte muss dann nicht mehr im Trial-and-Error-Verfahren kosten- und zeitintensiv erfolgen. Der Algorithmus hilft, aus der Vielzahl möglicher Varianten die mit optimaler Funktionalität vorherzusagen.

Der Ansatz des Fraunhofer FIT, modulare, sich selbst verbessernde Algorithmus-Plattformen für Design und Qualitätskontrolle von Leiterplatten einzusetzen, ist auch für viele weitere elektrische Systeme vorteilhaft. Auch dort werden Prozesse so optimiert, dass Zeit- und Produktionskosten in signifikanter Weise eingespart werden können.